## Factsheet GEMAC OVC SI80GEOVC10

## **Gigabit** Ethernet MAC **SystemVerilog** OVC VIP

Gigabit Ethernet Media Access Control (MAC) SystemVerilog OVC VIP is fully documented, off-theshelf component for the developers of the Gigabit Ethernet MAC. Full Programmability and versatility of the OVC enables connection to any standard IEEE 802.3 based GEMAC device and supports application of Stimulus to the generic microcontroller Interface as well as PHY Interface

The GEMAC OVC based VIP provides a concise, declarative mechanism to code the specification of sequences of events and activities of Gigabit Ethernet MAC Protocol. This methodology provides the best framework to achieve coverage driven verification.

GEMAC VIP is developed using the OVM Class Library that includes ovm\_sequence, ovm\_driver etc. base classes and capabilities to create modular, reusable components. This methodology combines automatic test generation, self-checking test benches and coverage metrics to significantly reduce the time spent verifying a design under test.

*Silicon Interfaces'* GEMAC core implements the Ethernet Media Access Control (MAC) protocol according to IEEE 802.3 specification. The MAC has a standard Gigabit Media Independent Interface (GMII) to connect to any PHY interface. A single channel MAC with PCI controller would provide an ideal solution for inexpensive NIC cards.

#### **Product Specifications**

- The OVM VIP can be adapted to test a standard Gigabit Ethernet MAC device in a Verification environment

- Separate set of tasks provided for Transmit as well as Receive sections in Full-duplex mode

- Extensive checking of the PHY Interface for the MAC

# Silicon Cores<sup>TM</sup>

Core to the Intelligent System<sup>™</sup>

### **Product Highlights**

- ☑ Fully OVM-compliant and completely configurable with SystemVerilog environment, as per user requirements and OVM user guide for OVC's.

- ☑ Accurately verifies IEEE 802.3 standard Gigabit Ethernet MAC specifications

- ☑ Application of Stimulus to the Generic Microcontroller Interface as well as PHY Interface

- ☑ OVM based transactions using monitors, checkers and scoreboards.

- $\blacksquare$  Supports scoreboard checking

- ☑ Built in Coverage model implemented for all transaction types

- ☑ Built in Monitors for protocol monitoring and checking

- ☑ Provides checking of valid Inter Packet Gap

- ☑ Support for checking of normal as well as VLAN tagged Packets

- ☑ Supports checking of Pause Frames

- Provides Checkers for Minimum and Maximum payload sizes, for both normal as well as VLAN tagged Packets

- ☑ Checkers to determine validity of Preamble bits along with SFD

- ☑ Separate Configuration file for Parameter definitions

GEMAC OVC 04/04/2008

Copyrights © 2002-2003 *Silicon Interfaces* Private Limited. All rights reserved. 606, Nirman Kendra, E. Moses Road, Mahalaxmi, Mumbai 400 011 India www.siliconcores.com and www.siliconinterfaces.com

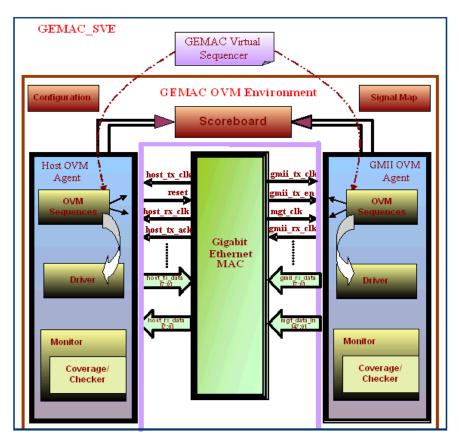

### **GEMAC OVM Environment**

#### **GEMAC DUT Description:**

The Gigabit Ethernet MAC is connected between the Microcontroller-based Host and Physical Layer. The Microcontroller serves as the Host (Link Layer), which receives and transmits Packets from and to the MAC. The other end of the MAC is connected to the PHY (Physical Layer).

The **OVC VIP** is built around the **DUT** as an epicenter. Constructs within monitor the interfaces and provide a detailed log on the transactions that take place to and from the **DUT**. Thus, just by looking for Successes or Failures within the log output, the function of the **Gigabit Ethernet MAC** could be easily and effectively validated.

#### **OVM Environment Description:**

**GEMAC Virtual Sequencer** has collection of OVM based virtual sequences to control **Host** as well as **GMII** sequences. Sequences are the stimulus data which is fed to the **DUT** through the **Driver**. The **OVC Class Library** provides the **ovm\_sequence** base class. These sequences are derived from the base class. The sequences body tasks are implemented with the specific scenarios to execute the sequences.

The **Driver** obtains data items from the sequencer for execution. The driver's role is to drive data items to the bus following the interface protocol. The **Driver** classes are derived from the **ovm\_driver** base class.

**Monitor** extracts signal information from the bus and translates it into events, structs, and status information. The **Monitor** functionality includes protocol checking and coverage collection.

A **Scoreboard** verifies the proper operation of the design at a functional level. It taps the information going in and out of the **DUT** and determines the **DUT** response according to the stimulus generated.

Contact: Email: info@siliconinterfaces.com Phone: (+91-22) 2491 3024; Fax: (+91-22) 2498 1379 In USA: (+1-408) 866 2458; Fax: (+1-408) 866 6586 In UK: (+44-20) 8543 4436; Fax: (+44-20) 8544 1311

**Notice:** Information in this document is indicative. Product specifications are subject to change without notice. *Silicon Interfaces* shall not be responsible for direct, indirect or consequential damages that may accrue through typographical errors or otherwise. No license, expressed or implied to any intellectual property rights is granted by this document. Product names mentioned herein may be trademarks and/or registered trademarks of their respective owners. Rights are hereby acknowledged.

Silicon Interfaces<sup>®</sup>

a software and vlsi design center

Silicon Interfaces is the world's answer to integrated solutions for Design Services needs for SOC, ASIC & FPGA for Wireless, Cable & Optical Networking, Fiber Channel & Inter-connect, Data Communications and Storage. Silicon Interfaces is operating since 1990 primarily in USA, Europe and Pacific Rim.

Copyrights © 2002-2003 *Silicon Interfaces* Private Limited. All rights reserved. 606, Nirman Kendra, E. Moses Road, Mahalaxmi, Mumbai 400 011 India www.siliconcores.com and www.siliconinterfaces.com